[ad_1]

The Area-Saving System within the PowerPAK 1212 reduces element counts and simplifies designs by requiring 50% much less PCB area than discrete units.

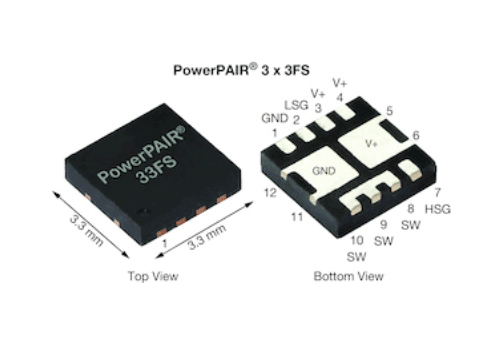

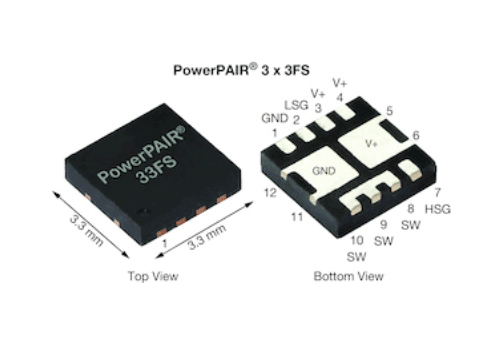

Vishay Intertechnology, Inc. has introduced the launch of a brand new 80 V symmetric twin n-channel energy MOSFET, which integrates excessive and low-side TrenchFET Gen IV MOSFETs right into a compact 3.3 mm by 3.3 mm PowerPAIR 3x3FS bundle. Designed for energy conversion in industrial and telecom purposes, the Siliconix SiZF4800LDT enhances energy density and effectivity whereas enhancing thermal efficiency, decreasing the variety of elements, and streamlining designs.

This twin MOSFET gives a space-efficient different to 2 discrete units sometimes used within the PowerPAK 1212 bundle, leading to a 50% discount in board area. It supplies an efficient resolution for synchronous buck converters, level of load (POL) converters, and half- and full-bridge energy phases in DC/DC converters for radio base stations, industrial motor drives, welding gear, and energy instruments. The SiZF4800LDT’s excessive and low facet MOSFETs are optimised for 50% obligation cycles, and its logic stage turn-on at 4.5 V simplifies driving circuits. The important thing options embrace:

- TrenchFET Gen IV energy MOSFET

- Symmetric twin n-channel design

- Flip chip know-how for optimum thermal administration

- Business-leading low on-resistance of 18.5 mΩ at 4.5 V, 16% and 54% decrease than the closest competitor

For enhanced effectivity in high-frequency switching purposes, the SiZF4800LDT boasts a low on-resistance instances complete gate cost — an important determine of benefit (FOM) for MOSFETs in energy conversion — of 131mΩ*nC. This low on-resistance and thermal resistance mixture permits it to deal with a steady drain present of 36 A, which is 38% increased than the closest competing system. The MOSFET’s distinctive pin configuration facilitates a simplified PCB format and allows shorter switching loops to scale back parasitic inductance. The MOSFET is totally Rg- and UIS-tested and is each RoHS-compliant and halogen-free. They’re at the moment obtainable in each pattern and manufacturing portions, with a lead time of 26 weeks.

[ad_2]