[ad_1]

Researchers at Yonsei College and Sungkyunkwan College have developed an answer processing methodology to manufacture wafer-scale transistor arrays utilizing molybdenum-disulfide.

Engineers have been making an attempt to develop extra environment friendly and cost-effective approaches for mass-producing digital parts and units. In current research, researchers have explored the chances of making electronics utilizing resolution processing strategies, which contain depositing supplies with electrical properties onto a floor from an answer.

Researchers at Yonsei College and Sungkyunkwan College in South Korea have developed an answer processing methodology to manufacture wafer-scale transistor arrays utilizing molybdenum-disulfide, an inorganic compound. Beforehand, the researchers showcased wafer-scale electronics using completely different solution-processed 2D supplies. Increasing on this analysis, the most recent examine aimed to optimize digital properties whereas making certain scalability.

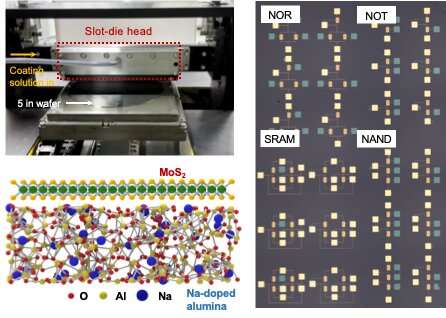

The crew employed a industrial slot-die printing course of to manufacture their wafer-scale transistors. This methodology includes depositing liquid supplies onto numerous substrates, together with glass, metals, or polymers. The scientists formulated inks comprising nanosheets of molybdenum disulfide and sodium-embedded alumina. Subsequently, they utilized slot-die printing to use these inks onto a substrate, forming semiconducting and gate dielectric layers. For reaching vital scalability, a slot-die coater, an industrial-level coating methodology, was employed to uniformly cowl solution-processed dielectric and semiconducting channel layers on a 5-inch wafer. The crew utilized a particular dielectric layer often called sodium-doped alumina to showcase high-performance electronics, enabling the best field-effect mobility as much as 100 cm2/Vs utilizing solution-processed MoS2 skinny movies.

Throughout the preliminary assessments, the transistors developed by the researchers showcased spectacular efficiency traits. They displayed common cost service mobilities of 80.0 cm² V⁻¹ s⁻¹ in field-effect transistor measurements and 132.9 cm² V⁻¹ s⁻¹ in Corridor measurements at room temperature. To additional exemplify the capabilities of their transistors, the crew utilized them to create numerous units, reminiscent of NOT, NOR, NAND, and static random-access reminiscence.

The researchers imagine that probably the most vital contribution of this work is introducing a recent avenue for high-performance, large-scale 2D material-based electronics via an industrial-level coating method. In future, the researchers intention to concentrate on broadening the vary of solution-processed materials candidates, encompassing numerous digital properties like digital sort and bandgap.

Reference: Yonghyun Albert Kwon et al, Wafer-scale transistor arrays fabricated utilizing slot-die printing of molybdenum disulfide and sodium-embedded alumina, Nature Electronics (2023). DOI: 10.1038/s41928-023-00971-7

[ad_2]